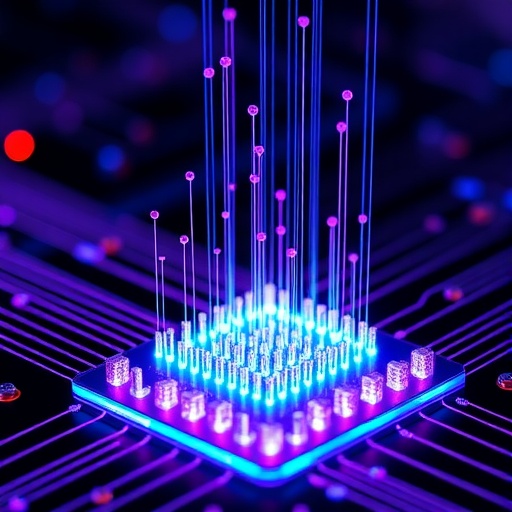

In an era increasingly defined by the insatiable demand for rapid computing and energy-efficient artificial intelligence, a groundbreaking advancement emerges from the realm of photonics—ushering in a new frontier for neural network inference hardware. Researchers led by Wu, Huang, Zhang, and their team have revealed a path toward scaling end-to-end photonic neural networks directly on-chip, a breakthrough that promises to revolutionize how AI computations are performed at the hardware level. This novel development addresses one of the most critical challenges in artificial intelligence hardware: marrying speed, power efficiency, and integration scalability into a single compact platform.

Traditional electronic-based neural networks, while powerful and ubiquitous, face deep physical and practical limitations as AI model sizes and computing demands continue to skyrocket. Electronic circuits suffer from intrinsic resistive losses and Joule heating, which severely bottleneck performance and energy consumption. Photonic systems, by contrast, leverage light to process information at the speed of photons—orders of magnitude faster than electrons—without the resistive losses that plague electrical circuits. The research team’s innovative work focuses on expanding this potential by designing an on-chip photonic network capable of performing the entire inference computation end-to-end, rather than offloading parts to electronics.

Central to their approach is the integration of scalable photonic components on a silicon photonics platform, which leverages mature complementary metal-oxide-semiconductor (CMOS) fabrication processes. This compatibility ensures that the photonic neural networks can be mass-produced in a cost-effective manner while benefiting from the precision and reliability of semiconductor manufacturing. The mainstream applicability of their solution lies not only in its technical merits but also in its practicality for future deployment in consumer electronics, data centers, and autonomous systems requiring low-latency AI inference.

The architecture hinges on an intricate interplay of optical modulators, waveguides, interferometers, and photodetectors, all arranged to replicate the matrix multiplications that lie at the heart of neural network inference. Unlike traditional electronic neural accelerators, which rely on transistor switching, the team uses phase modulation of coherent light signals propagating through silicon waveguides to encode and transform data. The coherent nature of the photonic signals enables interference patterns that effectively carry out multiply-accumulate (MAC) operations intrinsic to neural computations in a parallel and massively scalable fashion.

One of the core challenges the researchers tackled was mitigating optical noise and signal degradation over the chip scale, which previously limited photonic systems to small-scale demonstrations. By introducing innovative calibration schemes and feedback control loops embedded within the chip, their design maintains signal fidelity and dynamic range across deep photonic layers. This stability is essential for reliable AI inference, where small signal errors could cascade into incorrect predictions or data loss.

The demonstrated device achieves impressive throughput while drastically lowering energy consumption. Initial results indicate that their photonic neural platform consumes magnitudes less power per inference compared to state-of-the-art electronic AI accelerators, without sacrificing computational accuracy. This positions the technology as an enabling solution for edge AI applications, from wearable devices to autonomous vehicles, where power budgets are severely constrained yet real-time processing is vital.

Furthermore, the team’s end-to-end integration means that optical signal processing is seamlessly combined with electronic readout circuits and memory, all embedded in a monocular chip footprint. This holistic design departs from previous hybrid architectures that chained multiple separate photonic and electronic modules, introducing latency and system complexity. By refining the fabrication process so that active photonic elements coexist alongside electronic control and memory layers, the authors pave the way for truly integrated photonic neural processors.

Their work also addresses scalability concerns by demonstrating that their photonic neural network design can extend to deeper architectures, accommodating layers beyond tens of thousands of parameters without prohibitive footprint increases or signal interference. This scalability is critical, as contemporary deep learning models grow ever larger, demanding hardware capable of supporting complex inference without compromise.

Importantly, the research reveals the potential for real-time adaptability. By integrating fast tunable optical elements with control algorithms, the photonic network can dynamically reconfigure itself during operation, allowing it to respond to changing inputs or retrain on new data streams. Such adaptable photonic neural processors could be revolutionary for applications such as personalized healthcare diagnostics or on-the-fly data analytics in edge computing.

Integrated photonic neural networks also offer unique advantages in bandwidth and parallelism. Unlike electrical interconnects constrained by metal wiring density and signal interference, optical waveguides enable vast arrays of parallel channels with minimal crosstalk, significantly boosting effective data throughput. The team exploited these inherent advantages by designing multiplexed wavelength channels that operate simultaneously, further accelerating inference speeds.

Despite these remarkable achievements, challenges remain before widespread deployment becomes feasible. Fabrication yield and integration of high-quality optical components at large scale must be standardized, and efficient interfaces to electronic memory and control systems require further refinement. Nevertheless, the current breakthrough provides a compelling blueprint for the next generation of AI processors, blending photonics’ intrinsic speed and efficiency with silicon-based scalability.

The implications of scalable, end-to-end photonic neural networks extend well beyond AI inference. They suggest a paradigm shift in computing architectures, where light replaces electrons as the primary computation bearer, enabling vast savings in energy and improvements in speed. As AI systems become ubiquitous—from smart homes to autonomous machines—photonic integration could become the cornerstone technology underpinning these future intelligent environments.

In addition to hardware innovation, the demonstrated platform opens rich avenues for algorithmic co-design, where neural network architectures can be tailored specifically to exploit photonic hardware characteristics. This synergy between hardware and software promises to unlock previously unattainable performance levels in AI applications, catalyzing an entirely new class of energy-efficient, ultrafast intelligent systems.

In summary, the pioneering work by Wu, Huang, Zhang, and colleagues signifies a monumental leap toward practical on-chip photonic neural networks capable of executing full end-to-end inference. Their success charts a tangible course to scale photonic AI hardware without compromising performance or integration complexity. As this technology matures, it will fundamentally change the AI hardware landscape—ushering in a future where photonic processors enable smarter, faster, and greener AI solutions around the globe.

Article Title:

Wu, B., Huang, C., Zhang, J. et al. Scaling up for end-to-end on-chip photonic neural network inference. Light Sci Appl 14, 328 (2025). https://doi.org/10.1038/s41377-025-02029-z

Article References:

Wu, B., Huang, C., Zhang, J. et al. Scaling up for end-to-end on-chip photonic neural network inference. Light Sci Appl 14, 328 (2025). https://doi.org/10.1038/s41377-025-02029-z

Image Credits: AI Generated